A SLANG interpreter for SCAMP

Wed 10 August 2022

I made the interpreter by ripping the parser out of the compiler, making it produce an AST instead of assembly code,

and writing a recursive evaluator for the AST. It was way less work than writing

the Lisp interpreter, and it runs programs about 100x faster

than the Lisp interpreter. Read more

A Lisp interpreter for SCAMP

Wed 3 August 2022

Lisp has been the most recent step in my search for the ultimate SCAMP programming environment.

Unfortunately what I have so far is so slow that it's probably another dead-end. It's about 300x

slower than compiled SLANG code. Read more

The ultimate SCAMP development environment

Wed 15 June 2022

I've been thinking about what I want the SCAMP development workflow to look like for

this year's Advent of Code. At first I was planning to do it in FORTH, but I've tried to

get into FORTH several times and haven't got on with it. I like the simple REPL of FORTH but I very

much do not like the language. So the plan is to come up with a way to make a REPL for

SLANG. Read more

Advent of Code on my homemade CPU

Fri 31 December 2021

This year I've built a 16-bit CPU, along with custom operating system

and programming language. It runs at 1 MHz and has 64 KWords of memory. This December I used it to do Advent of Code. Read more

The case for SCAMP

Thu 2 September 2021

All of the SCAMP hardware is now mounted properly inside the case, with no Arduino or breadboard required.

I'm now well into the "long tail" of tasks on this project, where it takes increasingly large amounts of time to

produce increasingly small improvements. Read more

Play with SCAMP from the comfort of your browser

Mon 9 August 2021

Today I ported the SCAMP emulator to the web, using emscripten

to compile C to WebAssembly, and Xterm.js to provide the terminal

emulator. Read more

Porting Hamurabi to SCAMP

Fri 6 August 2021

That's right! 1968's most exciting video game release is coming to 2021's most disappointing CPU architecture.

Hamurabi

is a single-player text-based game in which you play the leader of ancient Sumeria for

10 years. Each year, you decide how much land to buy or sell, how much food to feed to the population, and how much land to plant with seeds. Occasionally

a plague comes along and kills half the population, or rats eat some of the harvest. Land values, harvest yields, and immigration rates

fluctuate unpredictably. At the end of the 10 years (if you haven't been forcibly removed from office already) your performance is evaluated. Read more

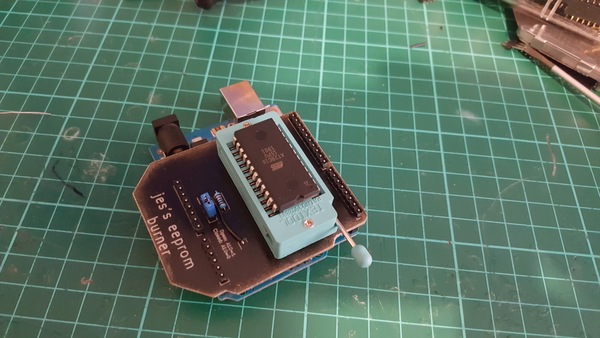

SCAMP update

Thu 24 June 2021

I've made a bit more progress on my SCAMP CPU. I/O performance is

improved significantly since last time, the CompactFlash card now lives on a PCB instead of a breadboard, I'm

using a real (ish) serial console instead of an FTDI cable, and I have a more

permanent power supply instead of the bench power supply. Read more

SCAMP has booted up to the shell for the first time

Sun 25 April 2021

I reached another good milestone on SCAMP this week: the physical hardware booted all the way up to the shell.

Granted, it only happened once, and I couldn't type any input once it got there. But it suggests that there are

no fundamental problems with the hardware design that will prevent the computer from working, which I am very happy about. Read more

The kilo editor

Sat 3 April 2021

Thanks to the excellent Build Your Own Text Editor tutorial,

SCAMP/os now has an editor. It's pretty bare-bones, but perfect for what I need. Read more

SCAMP is alive

Sun 21 March 2021

I have reached a good milestone on the SCAMP hardware: it can now execute code! It runs all the way through the

test program

correctly. Read more

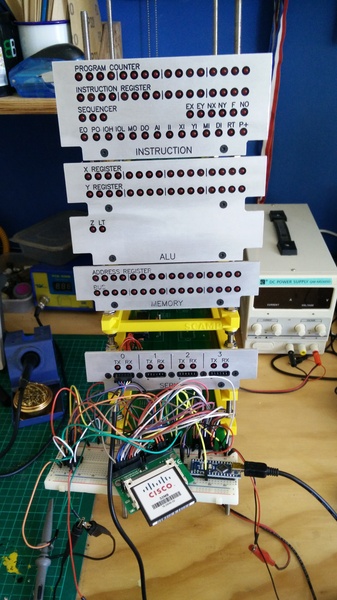

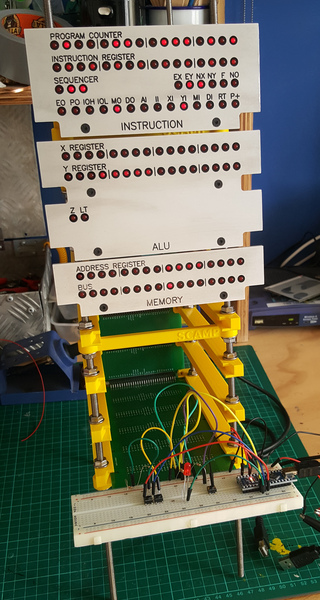

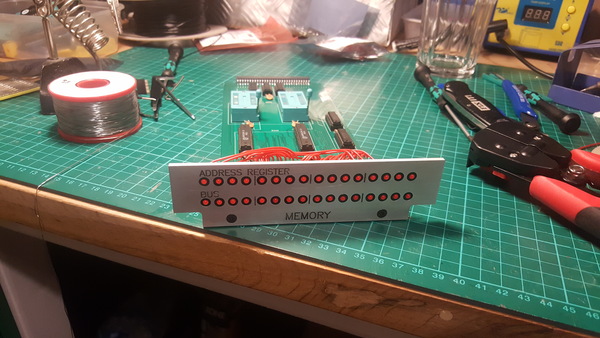

Front panels for SCAMP

Sun 28 February 2021

I've put together the memory card for the SCAMP CPU, including the front panel with LEDs to show

the bus contents and address register. Read more

The SCAMP kernel

Sat 27 February 2021

You might think it's a bit early to be working on an operating system, given that I don't have

a CPU to run it on. Maybe you're right. But working on software is easy and working on hardware

is time-consuming, so here we are. Read more

A compiler for SCAMP, and machine code profiling

Fri 19 February 2021

I've been working on a compiler for the SCAMP CPU. It compiles a language I'm calling "SLANG" (which just stands

for "SCAMP Language" pending a better backronym) into SCAMP assembly language. Read more

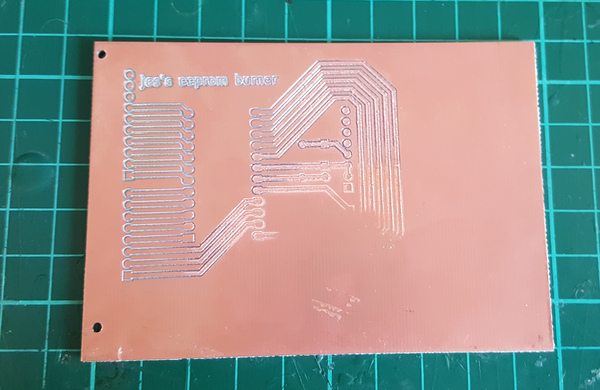

My second attempt at milling a PCB

Mon 15 February 2021

The day after my first attempt at milling a PCB, my new tooling

arrived (a 1 mm drill bit and a 10° engraving tool), so I had another go at making a PCB. Read more

My first attempt at milling a PCB

Fri 12 February 2021

I'm going to get most of the PCBs for SCAMP made by JLCPCB, but I'd like

to try to mill the backplane on the CNC machine because it is both large (expensive at

JLCPCB) and simple (single-sided, no vias, easy to make). Yesterday some small pieces of copper-clad

board arrived and today I had a first attempt to see what would go wrong. Read more

Making a start on the SCAMP ALU cards

Sat 6 February 2021

I'm pretty happy with the CPU design now and am ready to proceed to making it physically exist. I

am still finding the odd microcode bug, but these can be fixed at any time. I'm at least not finding any

architecture-level bugs. Read more

Designing the instruction set for my TTL CPU

Sun 31 January 2021

I (believe I) am making good progress on designing the TTL CPU. Most of the actual CPU design is

relatively stable now, and bug discoveries in the hardware design are infrequent, so now I get to move up

a level and work on the instruction set. After that, it's just the bootloader, operating system, and

application software. Oh, and the small matter of the physical hardware assembly... Read more

Progress on my TTL CPU design

Sun 24 January 2021

I want to make a CPU out of physical 74xx TTL chips. I have now implemented most of the parts using a subset of Verilog that

maps directly to TTL chips, and I wanted to write a bit about the design. Read more

Adventures in CPU design

Fri 15 January 2021

On Graham's recommendation, I recently bought an iCE40 FPGA and

have been learning a bit about how to use it. The iCE40 is good to get because there is good open-source tooling that supports it.

I was originally going to get the iCEstick evaluation board,

but there are other alternatives available more cheaply and with more logic elements. I ended up getting an iceFun

and have found it to be quite easy to use. The example projects are helpful. Read more